------------------无法下载或者链接失效请联系页面客服--------------------------

Verilog数字系统设计教程- 从入门到掌握

Verilog是数字系统设计中必不可少的一种硬件描述语言,可用于设计数字集成电路,数字信号处理系统以及其他任何类型的数字系统。通过本教程,您可以从入门到掌握Verilog,深入了解数字系统设计的基本原理与知识。

学习Verilog的重要性

随着现代电子技术的迅速发展,数字系统设计已经成为电子工程中不可或缺的一部分。在数字系统设计中,Verilog作为一种最流行的硬件描述语言,被广泛应用于芯片设计,自动化控制,数据通信等领域。

而学习Verilog不仅可以提高我们对数字系统设计的认知水平,更可以让我们在信息时代焕发新的活力。

本教程包含的内容

- Verilog语言的基本语法和数据类型

- 数字系统设计的基础知识,包括布尔代数,逻辑门,组合电路,时序电路等

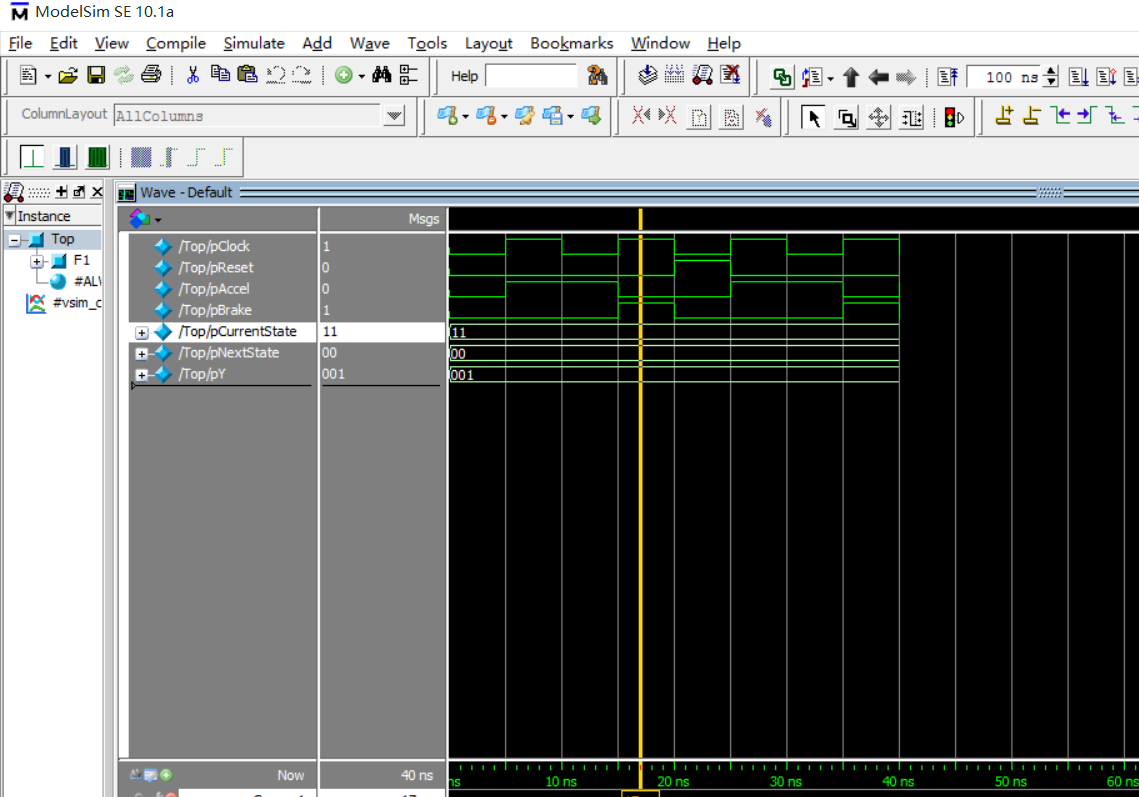

- Verilog建模的基本原理和方法,如Testbench验证等

- 设计复杂数字系统的实践经验,包括数码管显示系统,多功能电子钟设计以及基于FPGA的游戏设计

学习本教程的好处

通过学习本教程,您将能够掌握Verilog的基本语法和应用技能,更好地面对数字系统设计中的各种挑战。同时,本教程也提供了丰富的实例和案例,让您能够深入了解数字系统设计的原理和实践操作。

相信通过本教程的学习,您一定会在数字系统设计领域里迅速提升自己的技能和水平。

常见问题FAQ

- UU学院资源教程能否直接商用?

- 本站所有资源版权均属于原作者所有,这里所提供资源均只能用于参考学习用,请勿直接商用。若由于商用引起版权纠纷,一切责任均由使用者承担。更多说明请参考 VIP介绍。

- 提示下载完但解压或打开不了?

- 付款了无法下载怎么办?

- 链接地址失效怎么办?